Aperçu de la nouvelle version

### Points clés

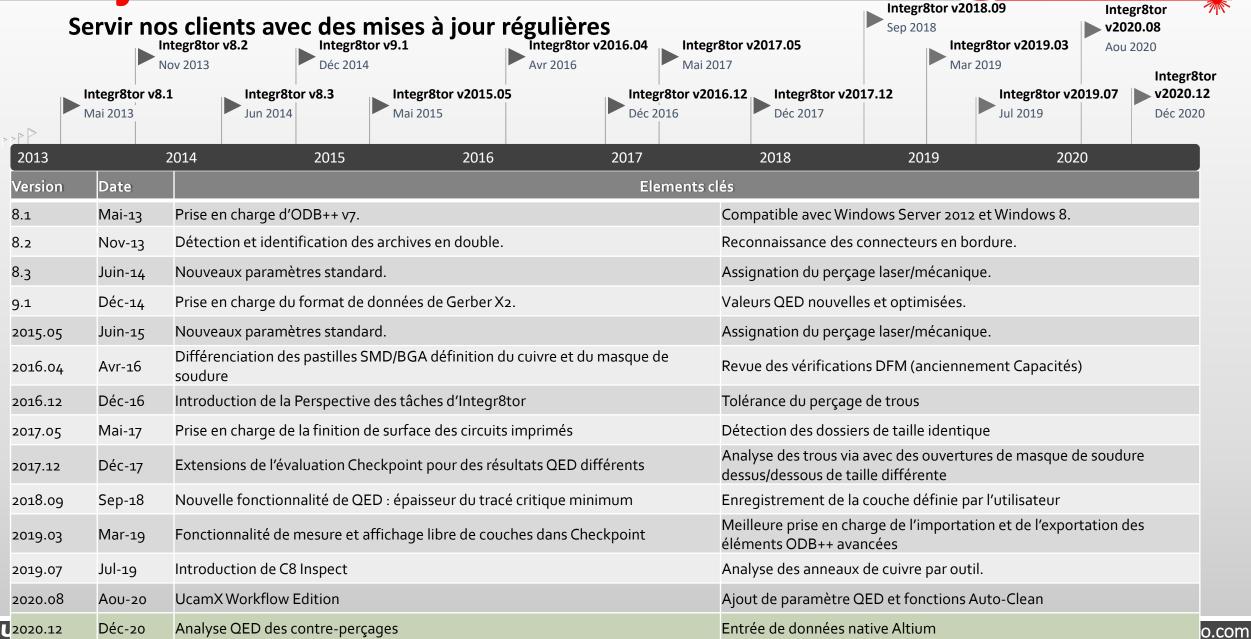

#### Les avantages sur la compétition ...

- Analyses QED des circuits avec contre-perçages

- Entrée de données CAO Altium (NEW!)

- Entrée de données DPMX (IPC-2581) (NEW!)

- Formatage conditionnel des valeurs QED basé sur les épaisseurs de cuivre.

- Et plus!

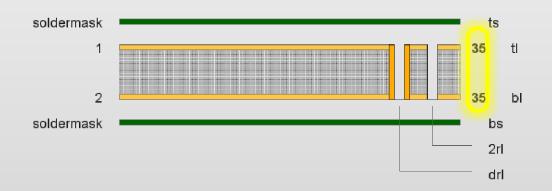

### **QED Contre-perçage**

# Analyses QED des circuits avec contre-perçages (Backdrilled)

- Entrée entièrement automatique des circuits contre-percés

- Analyse QED complète spécifique au contre-perçage

(Nouvelle option)

| INITIAL                             | FORMAT    | RENAMED   | FUNCTION  |

|-------------------------------------|-----------|-----------|-----------|

| 7770_Non_Switch_081015-bd-1-4.drl   | excellon2 | drl_1_4   | backdrill |

| 7770_Non_Switch_081015-bd-1-6.drl   | excellon2 | drl_1_6   | backdrill |

| 7770_Non_Switch_081015-bd-1-8.drl   | excellon2 | drl_1_8   | backdrill |

| 7770_Non_Switch_081015-bd-24-10.drl | excellon2 | drl_10_24 | backdrill |

| 7770_Non_Switch_081015-bd-24-12.drl | excellon2 | drl_12_24 | backdrill |

| 7770_Non_Switch_081015-bd-24-15.drl | excellon2 | drl_15_24 | backdrill |

| 7770_Non_Switch_081015-bd-24-17.drl | excellon2 | drl_17_24 | backdrill |

| 7770_Non_Switch_081015-bd-24-19.drl | excellon2 | drl_19_24 | backdrill |

| 7770_Non_Switch_081015-bd-24-21.drl | excellon2 | drl_21_24 | backdrill |

| 7770_Non_Switch_081015-bd-24-7.drl  | excellon2 | drl_7_24  | backdrill |

| 7770_Non_Switch_081015-bd-24-8.drl  | excellon2 | drl_8_24  | backdrill |

### Entrée de données

#### Entrée de données CAO Altium

- Integre le logiciel Altium Designer pour lire automatiquement les fichiers natifs .pcbdoc d'Altium

- Soyez le premier à proposer une offre !

(Nouvelle option)

### Entrée de données

#### Entrée de données DPMX (IPC-2581)

- Acceptez les données du standard émergent DPMX.

- Augmentez vos parts de marché en acceptant le format préféré de vos clients

(Nouvelle option)

### Formatage conditionnel QED

#### Basé sur les épaisseurs de cuivre

Les cellules colorées en rouge sur le rapport

QED PDF donne plus d'information quand

elles sont liées à l'épaisseur de cuivre.

(Ajout au rapport QED PDF)

```

61

Example:

62

<FormattingRule id="minimumtrack">

63

<Condition>lessthan</Condition>

64

<Value1>0.075</Value1>

65

<ThicknessRule id="base">

66

<Condition>lessthan</Condition>

67

<Value1>0.035</Value1>

68

</ThicknessRule>

69

</FormattingRule>

70

<FormattingRule id="minimumtrack">

71

<Condition>lessthan</Condition>

72

<Value1>0.1</Value1>

Critical

Copper to

73

<ThicknessRule id="base">

Trace

Copper

74

<Condition>between</Conditi

Width

75

<Value1>0.035</Value1>

76

<Value2>0.070</Value1>

mm

mm

77

</ThicknessRule>

>0.40

0.23

78

</FormattingRule>

79

<FormattingRule id="minimumtrack">

80

<Condition>lessthan</Condition>

<Value1>0.125</Value1>

81

82

<ThicknessRule id="base">

<Condition>greaterthan</Condition>

83

84

<Value1>0.070</Value1>

85

</ThicknessRule>

86

</FormattingRule>

```

### Epaisseurs de cuivre

#### QED avec épaisseur de cuivre de base et fini par couche

- Information d'épaisseurs de cuivre avec d'autres paramètres peut être mis dans le fichier gbrjob par exemple, ajoutez-le dans l'archive à analyser par integr8tor

- Simple, facile et efficace ...

(Ajout au rapport QED PDF)

| Files - Original |         |          |          |       |      |          |

|------------------|---------|----------|----------|-------|------|----------|

| Initial          | Renamed | Function | Position | Color | Thic | kness    |

|                  |         |          |          |       | Base | Finished |

## **Enregistrement temps passé**

#### Enregistrement du temps interactif passé sur un dossier

- Affichez le temps passé en interactif sur un dossier pendant une session

'To Ucam'

- Identifiez les données nécessitant systématiquement une intervention manuelle pour pouvoir donner des conseils sur les bonnes pratiques pour avoir des données standards.

(Ajout à Cockpit)

| Original Data                | Interactive Time |

|------------------------------|------------------|

| CDIpinv1.40vp (ID 18941).zip | 01:21            |

| 107665.zip                   | 00:00            |

| 107470.zip                   | 00:00            |

| 107154.zip                   | 00:00            |

| 107084.zip                   |                  |

| 106488.zip                   | 01:17            |

| 106046.zip                   | 00:00            |

| 105847.zip                   | 00:00            |

| 105832.zip                   | 00:00            |

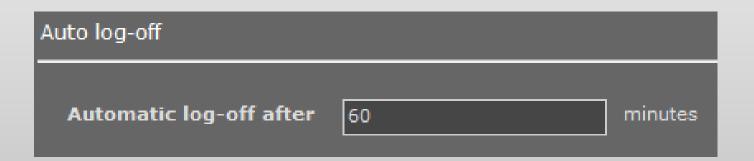

### **Utilisateur Cockpit**

#### **Auto log-off**

- Termine automatiquement les sessions Cockpit qui sont inactives ou périmées par exemple après une coupure sur le réseau.

- Ne plus être à court de licence Cockpit lorsque des utilisateurs oublient de fermer leur session.

(Ajout à Cockpit)

# Panneau d'assemblage

#### Analyse de la longueur de détourage

- Le détourage sur un panneau d'assemblage peut impacter considérablement le coût et les délais de livraison.

- Le nouveau champ QED « Depanel Rout Length » permet d'anticiper ce surcoût/délais.

(Ajout à Auto Analysis et rapport QED PDF)

|                                                                     | mm x mm mm mm                                               | THE PROPERTY AND ADDRESS. |       | Y Spacing | Spacing | Bottom<br>Border | Top Border | Right<br>Border | Left Border | Panel Size        | Original Image |

|---------------------------------------------------------------------|-------------------------------------------------------------|---------------------------|-------|-----------|---------|------------------|------------|-----------------|-------------|-------------------|----------------|

| Single PCB 178.021 x 143.000 15.000 5.000 5.000 3.000 3 x 2 1914.12 | Single PCB 178.021 x 143.000 15.000 5.000 5.000 3.000 3 x 2 | mn                        |       | mm        | mm      |                  |            |                 | mm          | mm x mm           |                |

|                                                                     |                                                             | 1914.126                  | 3 x 2 | 3.000     | 5.000   |                  |            |                 | 15.000      | 178.021 x 143.000 | Single PCB     |

## Vernis épargne

#### Ajout de nouvelles surfaces de finition et couleur de vernis

Ajout de nouvelles surfaces de finitions et couleur de vernis conformément à ce qui existe en production

(Ajout à Cockpit, Email Input Integration, Web Input Integration, Hotfolder Input Integration)

### Extension de l'analyse du vernis épargne dans le QED

• Une analyse approfondie par face sur les ouvertures dans le vernis épargne sur les vias. Permet d'éviter les mauvaises surprises en production.

(Ajout à Auto Analysis et rapport QED PDF)

### QED PDF

No Side

Covered

Vias ①

Through-hole vias that are either(partially) covered by soldermask on the top layer and (partially) free on the bottom layer or (partially) free

#### **Annotation QED PDF**

Nouveau style du rapport QED PDF avec info-

(Ajout au rapport QED PDF)

| bulles pour faciliter la lecture des informations | No | on the top layer and ( | partially) covered on the bottom layer. |  |

|---------------------------------------------------|----|------------------------|-----------------------------------------|--|

| du rapport.                                       |    |                        |                                         |  |

| (A:+ a a OFD DDF)                                 |    |                        |                                         |  |

Partly

Covered

Via Holes

One Side

Covered

Vias 1

Both Sides

Covered

Vias 1

#### **Changement dans QED PDF Summary**

Le tableau résumant les données essentielles sur le circuit a été optimisé.

(Ajout au rapport QED PDF)

| PCB Size            | 95 mm x 103.5 mm  | Customer Panel Size      |                            |

|---------------------|-------------------|--------------------------|----------------------------|

| PCB Thickness       | 1.6 mm            | Max. Aspect Ratio on PTH | 8.0                        |

| Copper Layers       | 6                 | Pressing Stages          | 1                          |

| Surface Finish      | unknown           | Drill Hole Density       | 2101 Holes/dm <sup>2</sup> |

| Solder Mask         | Both              | Testable Points          | 1508                       |

| Solder Mask Color   | unknown           | Min, SMD/BGA Size        | 0.28 mm                    |

| Legend              | No                | Via in Pad               | No                         |

| Legend Color        |                   | Stacked Vias             | No                         |

| Edge Connector Area | 0 dm <sup>2</sup> | Castellated              | No                         |

| Peeloff Mask        | No                | Anomalies                | No                         |

| Carbon Mask         | No                |                          |                            |

### Installez v2020.12

- L'installeur peut être téléchargé sur ftp://ftp.ucamco.com/Integr8tor

- Nous vous conseillons d'installer cette mise à jour dès que possible

- Si vous avez besoin d'informations complémentaires, veuillez contacter notre partenaire commercial local ou la Hotline d'Ucamco

- Nous vous remercions d'avoir choisi un produit Ucamco

Déjà tourné vers l'avenir

#### © Copyright 2021 Ucamco NV, Gent, Belgium. All rights reserved.

This material, information and instructions for use contained herein are the property of Ucamco NV. The material, information and instructions are provided on an AS IS basis without warranty of any kind.

Ucamco NV does not warrant, guarantee or make any representations regarding the use, or the results of the use of the software or the information contained herein.

Ucamco NV shall not be liable for any direct, indirect, consequential or incidental damages arising out of the use or inability to use the software or the information contained herein.

The information contained herein is subject to change without prior notice.

Revisions may be issued from time to time to advise of such changes and/or additions.

No part of this presentation may be reproduced, stored in a data base or retrieval system, or published, in any form or in any way, electronically, mechanically, by print, photoprint, microfilm or any other means without prior written permission from Ucamco NV.